Overview

Synopsys is one of the world’s leading EDA (Electronics Design Automation) tools provider and has verification, IPs and Software Security portfolios. Their tools are used by most of the Semiconductor companies across the globe to bring up their ASIC (Application Specific Integrated Circuit) and SoC (System on Chip) to power the present digital world.

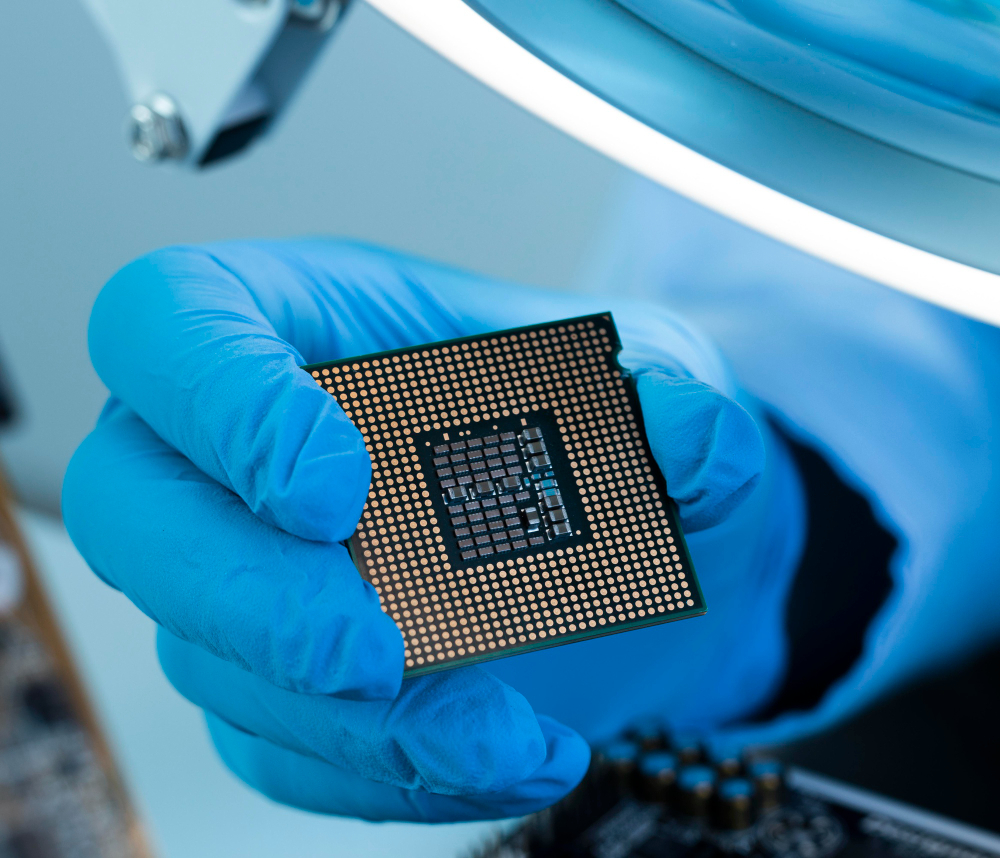

Modern digital needs like social media, e-commerce, ed-tech, advanced aerospace and defense applications like satellite communications and RF and data centers require advanced chips with extremely high processing and computing speeds. Having foreseen these demands, semiconductor giants such as Intel, SAMSUNG, Qualcomm, NVIDIA, ARM, AMD, Micron, Microchip etc., are competing each other by introducing high performance chips to meet the market needs at a faster pace.

Importance of Synopsys EDA tools in Chip design

They minimize the risk and reduces the trial-and-error costs. The chip cannot be altered once it is manufactured. Their designs are extremely complex and involves high development and R&D cost. The tools can diagnose complex physical problems as quantitative models, simulate circuit process in virtual software, and reproducing multiple effects in the chip development cycle. One of the highlights of Synopsys EDA suite is to simulate and optimize the PPA (Power, Performance and Area), which solves the multiple objectives and problems and reduces the cost of trial and error.

Chip designing Process

The chip designing process is divided into Front end Design and Back-end design.

Front-end Design:

Front end which is known as logic design involves the functional design of the chip. From defining the chip architecture to generating the netlist is the front-end design, which also involves a functional verification to verify the circuit functions and logic.

Design:

RTL creation can be performed using the Euclide and Synopsys RTL Architect is a predictive RTL design solution that provides early predictions of the impact of the RTL changes on your PPA.

Lint, CDC (Clock Domain Crossing) and RDC (Reset Domain Crossing)

RTL errors are very crucial in SoC design which may lead to design failure or even re-spins of the chip. Synopsys SpyGlass offers early RTL Analysis during the RTL design phase to avoid linting, CDC and RDC errors.

Simulation (Functional Verification)

Synopsys VCS tool is a widely popular tool for the formal verification to simulate the RTL design meeting its design specifications. VCS is capable of mixed language simulation, supports UVM, OVM VMM methodologies, and Verification IPs. All the gate level simulations and power simulations can be performed in VCS.

DFT – Design for Testability

DFT is a testing technique in IC design during the manufacturing process by implementing additional design features to ensure the designed circuit is free from any kind of manufacturing defects. Synopsys TestMAX DFT is a comprehensive tool which supports all essential DFT such as boundary scan, scan chains, core wrapping, test points and compression. They can be implemented using TestMAX manager for early validation of the corresponding RTL or with Synopsys Synthesis tools for generating the netlists.

Synthesis:

Design compiler and Synplify are the two Synthesis solutions from Synopsys for the IC designs and FPGA designs respectively, which are widely popular across the industry. Design compiler supports mixed language placement aware synthesis, optimization of multi voltage, low power synthesis, placement aware physical synthesis and multi-threading. Synplify has faster runtime, performance, area optimization for cost and power reduction, multi–FPGA Vendor support, incremental and team design capabilities for faster FPGA designs.

Back-end Design:

Back-end which is also known as Physical design involves process related design. The major activities are placing and routing the millions of transistors on a chip, to optimize the Power, Performance and Area.

Physical Design: Physical Design comprises of Floor Planning, Place and Route, Power planning, Low power analysis and Power estimation. All these can be achieved by using Synopsys IC Compiler.

Physical Verification: Correctness and reliability of the physical layout of the ICs are verified through a critical process of Physical Verification. The process involves verifying the design against a set of design rules to ensure that the final product functions are intended. Synopsys IC Validator can perform the Design Rule Checks (DRC), Layout versus Schematic (LVS), Electrical Route Check (ERC), GDS comparison, Netlist-to-Netlist verification, Layout vs Layout and Antenna Checks.

Sign-off: Synopsys is a leading solution provider in the design sign-off innovations, which addresses the challenges of complex design, scale and new requirements for chip design on advanced processor nodes. The sign-off is done with Synopsys IC Compiler II.

Synopsys IP Solutions:

Synopsys Silicon IPs are the most popular and has a wide portfolio of solutions with proven results across the industry. Logic Libraries, Embedded Memories, Interface IPs, Embedded Processors and Subsystems fall under the IP portfolio. The IPs are optimized for a wide range of market segments like Internet of Things, Automotive, Artificial Intelligence, 5G Mobile and Data Center.

Synopsys Manufacturing Solutions:

Synopsys is a market leader in offering the Silicon Manufacturing and Silicon Life cycle management solution. It includes TCAD (Technology Computer Aided Design), Mask Synthesis and Manufacturing Analytics. The Synopsys manufacturing solutions are customized for expertise in IC design, mask synthesis, process modelling, on-chip test and monitoring techniques and cloud-based analytics.

How Foundries are benefiting with Synopsys

Synopsys is collaborating with Intel for developing interface and Foundation IPs for Intel Foundry’s latest process for their high-power efficiency System-on-Chips. They have been collaborating for decades to accelerate the design productivity. Intel and Synopsys together are driving the next gen system innovations for a wide range of applications like High Performance Computing (HPCs), Automotive, Mobile and Aerospace.

Taiwan Semiconductor Manufacturing Company Limited, which contributes more than 50% of the market share in chip manufacturing is also collaborating with Synopsys by using their silicon IPs, EDA Tools and multi-die system design flow and Photonic IC design flows for their advanced process technologies. This collaboration of over 20 years have helped them deliver high quality interface IPs and foundation IPs for their process technology from 180nm to 3nm for applications like HPCs, AI, Automotive and Mobile.