Next-Generation RTL Design and Synthesis

Synopsys’ RTL design and synthesis solutions, including RTL Architect™ and Design Compiler® NXT, enable engineers to achieve superior power, performance, and area (PPA) optimization across all process nodes, especially at advanced nodes like 5nm and below. RTL Architect™ provides predictive insights during the design phase, allowing early optimization of power, performance, and area, while Design Compiler NXT delivers faster runtimes, enhanced quality of results (QoR), and precise timing correlation with IC Compiler™ II.

Advanced Power and Low-Power Design

The Design Compiler family includes Power Compiler for low-power synthesis and optimization, helping to meet the demands of power-sensitive designs. Additionally, the extensive Synopsys IP Library offers a broad selection of synthesizable IP solutions, while integration with TestMAX ensures efficient, high-quality manufacturing tests. Formality® provides robust equivalence checking to guarantee correctness throughout the design process.

Unified RTL-to-GDSII Flow

As part of the Synopsys Digital Design Family, Fusion Compiler™ offers a unified RTL-to-GDSII flow built on a single scalable data model. By combining best-in-class engines for synthesis, placement, routing, and timing within a unified optimization framework, Fusion Compiler enables faster time-to-results and industry-leading QoR, making Synopsys the trusted partner for next-generation chip design.

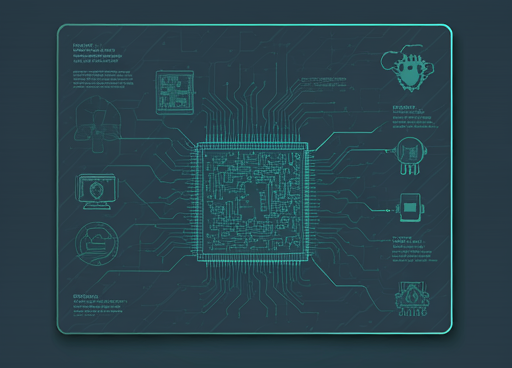

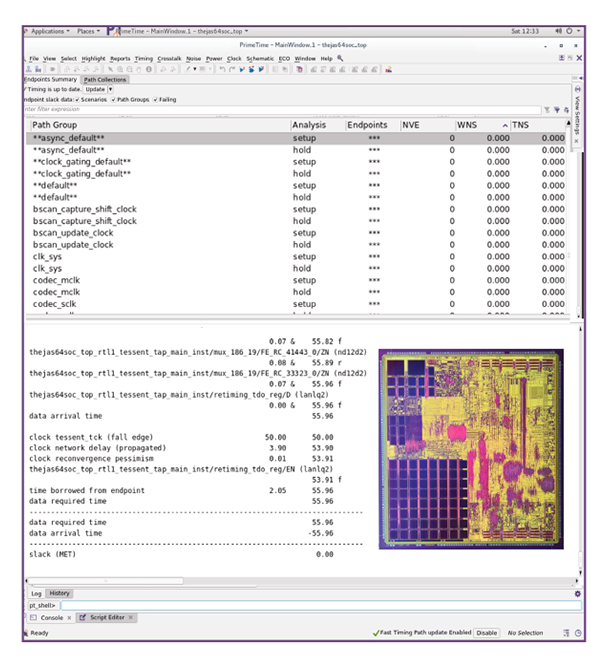

C-DAC

Synopsys PrimeTime helps achieve timing closure with a tight correlation between pre and post silicon results in the design of the fully indigenous 64-bit VEGA Processor based SoC, THEJAS64.