Quell Reliability Issues from the Start

As new device structures and process variants emerge, optimizing PPA (power, performance, and area) becomes more challenging, particularly at advanced process nodes where traditional modeling often falls short in capturing all real-world effects on silicon. To tackle potential reliability issues early, Synopsys offers enhanced coverage through memory-specific electrical rule checking, fast chip-level electromagnetic and IR analysis with power delivery network assessments, as well as functional safety solutions compliant with ISO 26262. Additionally, Synopsys provides multi-die system design tools and comprehensive silicon lifecycle management, ensuring robust, scalable designs.

Explore Other Product Capabilities

Meet PPA Demands In A Hyper-Convergent Era

Synopsys accelerates hyper-convergent memory design with fast PPA optimization and AI-driven simulations

Achieve Faster Turnaround Times for Hyper-Customized Designs

Synopsys speeds memory design with fast simulations, AI optimization, and early analysis, reducing risks and time-to-market

ReferencesSynopsys References

C-DAC

Know MoreResources

Defensics Fuzz Testing

Defensics® fuzz testing is a comprehensive, automated black-box solution that empowers organizations to identify and remediate security vulnerabilities in their software. Through its systematic and…

Introducing the Synopsys EDA Data Analytics Solution

Synopsys EDA Data Analytics Solution harnesses design and manufacturing data with advanced analytics and machine learning. It optimizes design processes, enhances product quality, and accelerates…

RTL Architect: Physically Aware RTL Design for Superior PPA Optimization

The RTL Architect solution is the industry’s first physically aware RTL design system that significantly reduces the development cycle and delivers superior quality-of-results. RTL Architect…

EDA (Electronic Design Automation) Explained

Electronic Design Automation (EDA) is a market segment encompassing software, hardware, and services aimed at defining, planning, designing, implementing, verifying, and manufacturing semiconductor devices, or…

Synopsys IP Portfolio: Silicon-Proven Solutions for IC Design

Synopsys, a leading provider of semiconductor intellectual property (IP), offers a comprehensive portfolio of silicon-proven solutions for integrated circuit (IC) design.

VCS: Industry’s Highest Performance Simulation Solution

The Synopsys VCS® functional verification solution is the primary verification solution used by most of the world's top 20 semiconductor companies. VCS provides the industry's…

Formality: Independent Formal Verification for Synthesis Results

Independent formal verification of Design Compiler and Fusion Compiler synthesis results, with built in intelligence delivering the highest verifiable QoR. Formality is an equivalence-checking (EC)…

Synopsys IC Validator: Scalable Physical Verification for All Nodes

Synopsys’ IC Validator physical verification is a comprehensive signoff solution improving productivity for customers at all process nodes from mature to advanced. The IC Validator…

Synopsys Design Compiler NXT: Next-Gen Synthesis for Advanced Nodes

Synopsys Design Compiler® NXT is the next step in the evolution of the industry leading Synopsys Design Compiler family. Building on the industry-standard Synopsys Design…

Synopsys FPGA Tools: Fast Synthesis & Debug for Optimized Design

The Synopsys FPGA design tools are comprised of synthesis and debug tools that enable designers to quickly deliver competitive products to market with the lowest…

IC Compiler II: Industry-Leading Place and Route for Next-Gen Designs

IC Compiler™ II is the industry leading place and route solution that delivers best-in-class quality-of-results (QoR) for next-generation designs across all market verticals and process…

Synopsys Verdi: AI-Powered Debug and Verification Management Platform

The Synopsys Verdi® debug and verification management platform is an all-encompassing solution designed to streamline and enhance your design entry, debug and verification management. With…

TestMAX DFT: Advanced Design-for-Test Solutions by Synopsys

Synopsys TestMAX DFT is a comprehensive, advanced design-for-test (DFT) tool that addresses the cost challenges of testing designs across a range of complexities. TestMAX DFT…

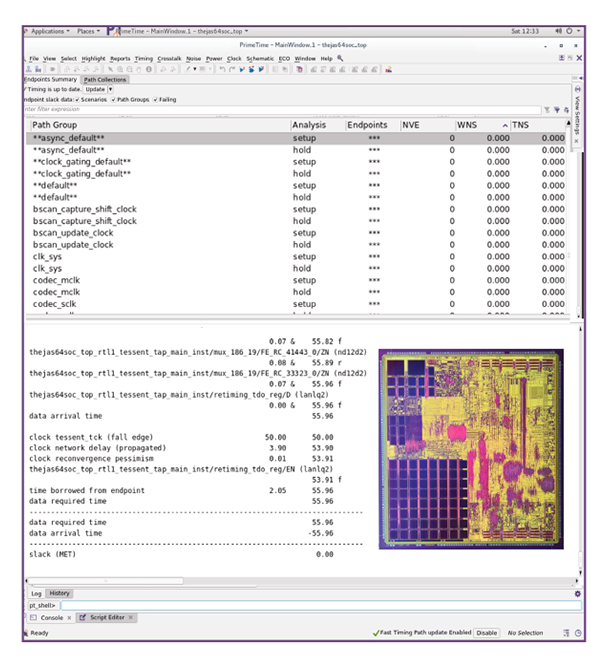

PrimeTime: High-Performance Timing Signoff with Multi-Scenario Analysis

Signoff users have a few key requirements for their signoff tool of choice: runtime and capacity to handle their largest chip size requirements, efficient multi-scenario…

PrimePower RTL to Signoff Power Analysis

The Synopsys PrimePower product family enables accurate power analysis for block-level and full-chip designs starting from RTL, through the different stages of implementation, and leading…

Synopsys StarRC: Gold Standard Parasitic Extraction Solution

Synopsys StarRC™, the Gold standard parasitic extraction solution, is a key component of the Synopsys Digital Design and the Synopsys Custom Design Families. Synopsys StarRC…